In RAHDG 438 we’ll Focus on designing different types of digital systems using Verilog language code then we simulate those in the Quartus software and at the end we do the implementation. It includes Design and analysis of latches and flip-flops. Number of digital designs have been designed in Verilog language to make you understand them better.

This course goes over different learning objectives in Verilog such as Fundamental Verilog Construct, Creating simple designs and developing Verilog test environment of significant capability and complexity. The design and analysis of synchronous state machines. Each topic will have many examples which goes over them briefly with different parts. By end of each chapter there will be a quiz for you to test your understanding of that specific chapter.

Core subject of this course is digital design flow. Topics include operators, Blocking and non-blocking assignments, RTL coding process, registers, flip flop, and latches. By end of the course, you should be able to design, simulate, implement, and troubleshoot our Verilog codes using appropriate techniques and test bench.

This course is mostly for academic level Engineering students in different universities around the world.

Since you would be having a lifetime access to this course you would be able to revisit during your career as year passes to refresh your memory.

Instructor

The instructor of this course is Mehrad Nahouri. He has an Associates in Electrical Engineering concentration on digital field and is a lecturer at Rahsoft.

What is the target audience?

- This course is for students working in Verilog field.

- Undergraduate students

- Electrical Engineer

- Computer Engineer

- Graduate students taking Verilog course

- Researchers in Verilog field

Course content

- Basic Concepts of Digital

- State Diagrams

- Moore vs Mealy Model

- Flip Flop

- JK Latch

- SR Latch

- Verilog

- Registers

- Counters

- Node Finder

- Multiplexer

- Quartus Simulation

- Functional Block Diagram

- ALU

- Always@

- FSM

Who this course is for:

- Electrical Engineers

- Computer Engineers

- Electrical Engineering Students

- Computer Engineering Students

Introduction

Introduction

Topic

State table

Sequential Logic

Moore Model

Mealy Model

Moore or Mealy

Moore Model

Moore Model

Moore Model

Moore Model

State Table

State table

State Diagram

State Diagram

State Diagram

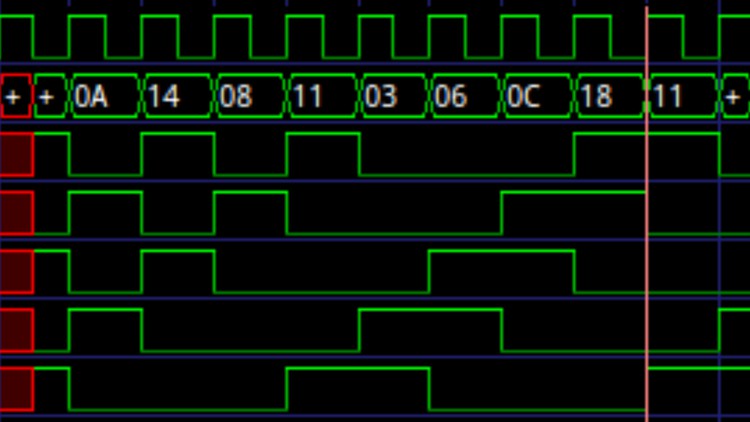

Timing Chart

Timing Chart

Design Procedure

Design Procedure

Typical Sequential Circuit

Sequence Detector

Design of Sequence Detector

Design of Sequence Detector

Design of Sequence Detector

Design of Sequence Detector

Design of Sequence Detector

Design of Sequence Detector

Design of Sequence Detector

Design of Sequence Detector

Design of Sequence Detector

Design of Sequence Detector

State Assignment

State Assignment

State Assignment

Other Flip Flops

SR FF Tables

JK FF Tables

TFF

TFF

Sequence Detector

Sequence Detector

Sequence Detector

Sequence Detector

Sequence Detector

Sequence Detector

Sequence Detector

Sequence Detector

Sequence Detector

1 Bit Register

4 Bit Register

4 Bit Register

Shift Registers

Shift Registers

Serial vs Parallel Addition

Shift Register with Parallel Load

Shift Register with Parallel Load

Counters

Synchronous Binary Counters

Synchronous Binary Counters

Synchronous Binary Counters

Synchronous Binary Counters

Up/Down Binary Counters

Up/Down Binary Counters

BCD Counters

Synchronously Reset and Load 9

Synchronously Reset on Terminal for count of 6

Synchronous Binary Counters

Row Matching Example

State Optimization

Ripple Counter

Ripple Counter

Minimal Cost and risk

State Encoding

2

Installing Quartus

New Project in Quartus

Programming in Quartus

Operator Types

Designing with Coding

Running a program in Quartus

Node Finder

4 Bit Full Adder

Designing Full Adder

Running Full Adder

Important Notes about Verilog

Different methods of designing in Verilog

Verilog Statements

Designing Systems using verilog

Running a System in Verilog

Multiplexer

Running a Multiplexer in Verilog

Running a Multiplexer in Verilog

Designing a 4:1 Multiplexer

Implementing a Multiplexer

Running a Multiplexer in Verilog

Designing a 4 bit multiplexer

Designing a Decoder

Programming a Decoder

Running a Decoder in Verilog

3

Conditional Operation

Functional Block Diagram

Example of FBD

Logic Expression Example

Logic Expression example

FBD Circuit

Tri-State Buffer

Relational Operators

Other Comperator Versions

Calculational Units

Designing ALU

Programming ALU

Running an ALU

Showing the operator results in Binary Systems

Result Operations

ALU Designing

Programming ALU

Running ALU Program

Other Methods of using Sequential Statement

Running ALU Program

IRE Structure

Programming IRE

Running IRE

Changing the designs namings

Redesigning Full Adders

Programming Full Adders

Running Flip Flop Program

4

Designing Module in parameter way

Designing 4 bit module

12 bit input module

Running 12 Bit Input Module Program

Running 12 bit input module

Latch and flip flop

Always@

Blocking assignments

Non Blocking assignments

Orders in always structure

Orders in always structure (parallel form)

Designing a custom flip flop

Programming a custom flip flop

Synchronous and Asynchronous description

Using always structure in Quartus

Register with load enable

Programming Register with load enable

Simulating Register with load enable

Making new modules using always structure

4:1 Multiplexer

Simulating 4:1 Multiplexer

Shift Registers

Programming Shift Registers

Simulating Shift Registers

Getting new outputs by giving inputs to the circuits

Shifting to the right

Running a shift to right

Simulating the new designed circuit

Universal shift register

5

Counters

Running a Counter

Generic Memory

Programming a memory

Simulating memory

Intro to FBD

Comparators

FSM

FBD

Programming FBD

Mealy FSM flowchart

Programming a mealy FBD

Simulating a FBD

Running a FBD

Simulating a Mealy FBD

Finding the FDB and FSM Flowchart based on the program

Moore FSM

Designing the FBD